白皮書|新型光鏈路提供完整的微波數(shù)據(jù)轉(zhuǎn)換接口,保證系統(tǒng)范圍的確定性

http://m.sharifulalam.com 2022-08-09 09:58 來源:Teledyne e2v

試想一下,是否有可能使用光纖互聯(lián)而不是銅線互聯(lián),建立多通道微波無線電系統(tǒng)?這種設(shè)計的優(yōu)點包括:

- 通過光纖簡化流采樣、控制和配置數(shù)據(jù),以及參考時鐘和同步信號的無線電前端設(shè)計和信號分布,并減少線纜的重量

- 在未來的無線電設(shè)計中無需進行銅介質(zhì)的信號布線,提供了更高的架構(gòu)自由度和靈活性,同時減少了串擾和信道間干擾,從而獲得更高的性能

- 光學(xué)概念證明可將前端模擬設(shè)計與后端數(shù)字信號處理分離,預(yù)示著由先進電子波束轉(zhuǎn)向引領(lǐng)的增強操作全數(shù)字天線時代的到來

本文將詳細介紹 Teledyne e2v 公司用于驗證光鏈路假說的實驗方法,并評估其發(fā)展現(xiàn)狀。

如今,全球數(shù)據(jù)中心廣泛地使用大量的光鏈路,因此乍一看這種光纖傳輸?shù)脑O(shè)想可能不是特別具有創(chuàng)新性。右 邊的方框里展示了使用光纖的主要優(yōu)點。

光纖的優(yōu)點

- 增強性能——沒有串擾,EMI 為 0

- 長距離通信 >> 20 m

- 減少重量,提高信號密度

然而,在無線電設(shè)計的領(lǐng)域中,我們需要解決一些新的工程挑戰(zhàn)。需要強調(diào)的是,這個方案旨在傳輸模擬信號環(huán)境和數(shù)字域的所有信號,因此必須處理低速控制信號和參考時鐘分布,最關(guān)鍵的是,必須確保確定性的多通道同步。原因在于,如果要實現(xiàn)理想的電子波束轉(zhuǎn)向,就必須保持信號空間(相位)的信息。

我們將討論如何高效使用 FPGA 的數(shù)字資源實現(xiàn)實驗數(shù)據(jù)編碼和解碼引擎的高級架構(gòu)。我們還將詳細介紹項目通常會遇到的挑戰(zhàn),以及如何維持系統(tǒng)范圍里的確定性。好消息是這個方案已被證明是可行的。讀者將深入了解這個 Teledyne e2v 新興微波軟件化能力的重要部分,之前的MWJ1文章首次討論了這個問題。

1 能否通過光纖實現(xiàn)確定性數(shù)字相位陣列控制?, MWJ 2021 年 11 月

項目目標

到目前為止,有兩個基于銅線的串行接口被用于連接寬帶數(shù)據(jù)轉(zhuǎn)換器和數(shù)字信號處理器。它們是行業(yè)標準JESD204 鏈接和 Teledyne e2v 的 無 需 許 可 證 的ESIstream 系統(tǒng)。

盡管光數(shù)據(jù)鏈路在現(xiàn)代的全球?qū)拵?yīng)用中有廣泛的應(yīng)用,但迄今為止,在無線電前端設(shè)計領(lǐng)域中,很少有人努力用它取代傳統(tǒng)的銅線設(shè)計。這里提出的數(shù)字光纜(ODH)項目旨在探索一種光學(xué)數(shù)據(jù)鏈路橋接的樣機的能力和局限性,需保證 4 種系統(tǒng)信號的可靠傳輸。它們是:

- 參考時鐘

- 所有頻率小于 100MHz 的單端信號,包括 SPI 和通用 I/O(GPIO)

- 用于實現(xiàn)系統(tǒng)范圍確定性采樣的專利的同步信號

- 數(shù)據(jù)轉(zhuǎn)換器的采樣數(shù)據(jù)

在 Teledyne e2v 的數(shù)據(jù)轉(zhuǎn)換器的領(lǐng)域中,確定性(即抑制不必要的偽隨機亞穩(wěn)態(tài))通過一種被稱為同步鏈的新型方法得以保證。同步鏈包含一個簡單的單沿同步信號的分布和一個同步標志,使龐大的轉(zhuǎn)換器并行系統(tǒng)保持同步。然而,使用銅介質(zhì)時容易解決的問題,在使用光纖傳輸時變得更具挑戰(zhàn)性。

我們設(shè)計了一種基于光纖的實驗樣機,以評估其作為銅線傳輸?shù)奶娲返倪m用性,并確定溫度和其他環(huán)境因素對其性能的影響。

在最初的實驗階段,物理光纖鏈路的長度是 10 米,使微波射頻模擬端和數(shù)字處理域分開適當?shù)木嚯x。

ODH實現(xiàn)

這個項目開始階段的主要挑戰(zhàn)有兩點:

- 最重要的是保證相對慢速的控制信號的可靠傳輸

- 傳輸無錯誤的確定性同步信號至多個轉(zhuǎn)換器,保證系統(tǒng)級確定性和同步采樣。這一點目前仍在實驗中。

先前的光纖鏈路的方案已支持控制信號和數(shù)據(jù)的傳輸。值得注意的是,英國林肯大學(xué)的一篇論文描述了一個基于 FPGA 的項目2,可組合 SPI 和 GPIO 數(shù)據(jù)并通過單一的光纖鏈路發(fā)送。

這篇論文描述了用于擴展傳輸距離的數(shù)據(jù)編碼的方法,并闡述了面臨的挑戰(zhàn)。先前的結(jié)論是:

- 注意建立可靠的鏈路同步,需要主參考時鐘。

- 編碼是成功的關(guān)鍵因素。在所述的例子里,8b/10b編碼被證明比其他更簡單的編碼方案(例如異或(XOR)或格雷碼)更合適。

- 最后,如果延遲很重要,例如對于這個實驗工作,作者詳細說明了如何重新同步鏈路以補償已知的系統(tǒng)延遲。

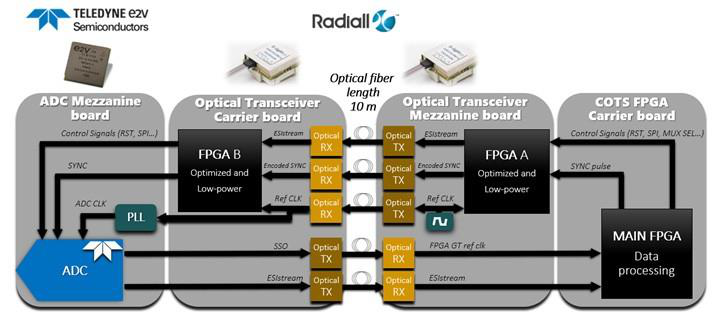

圖 1 數(shù)字光纜的概念設(shè)計

之前的工作奠定了如今的樣機的基石。我們提出了一種新的解決方案(圖 1),將低成本、低功耗的可編程邏輯器件(這里是 FPGA)配置為簡單的編碼引擎,以格式化、聚合和序列化從系統(tǒng) GPIO 和 SPI 消息直接生成的慢速控制向量。接著,編碼的消息向量和參考時鐘、離散編碼的同步信號一起通過三路并行光學(xué)線路傳輸。

2 跨通道同步由于亞穩(wěn)態(tài)而變得更加復(fù)雜。亞穩(wěn)態(tài)是一種數(shù)字系統(tǒng)固有的偽隨機行為,可通過精巧的設(shè)計來緩解。

實驗實現(xiàn)

我們的樣機基于現(xiàn)有的高端 IC 評估系統(tǒng)。我們選擇了一個包含了 EV12AQ600 的高級微波前端板卡的系統(tǒng)。這款四通道、12 位 6.4Gsps 的寬帶射頻 ADC 支持最高6.4GHz 采樣,為樣機提供了基于 FMC 的目標 ADC。EV12AQ600 直接安裝在一塊強大的信號處理(DSP)板卡上,使用標準的 FPGA 板卡格式(FMC)連接器。FMC為現(xiàn)有的互聯(lián)提供了有用的物理分隔,因此是改進的基于光纖的數(shù)字傳輸層的理想接口,如圖所示。

考慮到所需的各種數(shù)字控制和時鐘信號需通過 FMC 接口橋接,我們需要三個離散的光纖通道以控制發(fā)送到遠程接收端 ADC 的信號。此外,我們還需要另外兩個通道處理發(fā)回 DSP 板卡的數(shù)據(jù)和 SSO 通信。

我們的目標是實現(xiàn)一個實用的方案,因此需要尋找一款低成本、低功耗的可編程邏輯器件(PLD)。經(jīng)過市場調(diào)研,Artix 7 FPGA 成為代碼引擎的合適的選擇。參考圖 2 所示的系統(tǒng)分區(qū),很明顯對于未來的設(shè)計,可以很容易地將編碼引擎資源和 DSP FPGA 合并以降低成本。目前,我們只使用了不到 5%的 Artix 7 的資源。這是一款易于使用的樣機,可方便地進行編程,因此用戶可在設(shè)計的早期階段保持編碼引擎為離散模塊。

還需注意,我們需要遠程訪問參考時鐘,因此樣機的解碼端需要一個本地的時鐘發(fā)生器。物理層是通過 Radiall D-lightsys® VCSEL 光纖驅(qū)動器實現(xiàn)的。這個驅(qū)動器可支持從 100MHz 到 10GHz 的數(shù)據(jù)率,并在此范圍內(nèi)具有出色的時鐘抖動性能。Radiall 的堅固耐用的 D 光組合提供三種數(shù)據(jù)率等級(10Mbps、5Gbps 和 12Gbps)和多個封裝選項。這些器件被配置為四通道雙工收發(fā)器或 12 通道單工接收器/發(fā)射器。驅(qū)動與協(xié)議無關(guān),可提供標準LVDS 和 CML 電氣接口。

兩個關(guān)鍵的系統(tǒng)挑戰(zhàn)

這款樣機有兩個核心挑戰(zhàn),它們是:

- 對非切換同步信號編碼,以建立可靠的系統(tǒng)級光纖同步鏈解決方案,保證確定性

- 保證全速率鏈路鎖定

提供系統(tǒng)范圍的確定性同步

我們已在之前的幾篇論文里介紹了同步鏈。如前所述,如果要完全用光介質(zhì)替代銅介質(zhì),同步鏈是成功與否的關(guān)鍵因素。

在光纖上實現(xiàn)可靠的同步分布的挑戰(zhàn)是,同步信號通常是一個相對慢速的信號,其邏輯電平變化大約為 10ns。考慮到同步信號的“無時鐘”特性,它的精確的電平變化如何通過光纖傳輸?

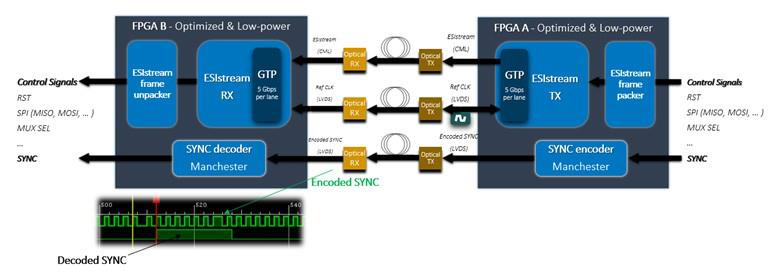

曼徹斯特編碼是一種簡單的相移鍵控技術(shù),可提供一種合適的解決方案。二進制數(shù)據(jù)與時鐘相位有關(guān)(圖 2),可有效保證中位電平轉(zhuǎn)換,有助于保持直流平衡(銅介質(zhì)接口)并提供規(guī)律的數(shù)據(jù)邊沿來源,以確保光纖鏈路保持鎖定并可區(qū)分出 SYNC 的有效性。

圖 2 SYNC 邊沿的曼徹斯特編碼

曼徹斯特編碼容易通過異或(XOR)系統(tǒng)所需的 SYNC 信號和參考時鐘實現(xiàn)。盡管這里可以看到在 SYNC 信號有效之前有一個穩(wěn)定的零數(shù)據(jù)流,但在半個參考時鐘周期內(nèi),接收端成功識別了 SYNC 由低到高的轉(zhuǎn)變。

順便說一句,延遲可能會影響系統(tǒng)級同步,這也是保證銅介質(zhì)鏈接的確定性的挑戰(zhàn)之一。使用光纖時,延遲比使用銅線時低幾個數(shù)量級。因此,對于大多數(shù)的應(yīng)用,調(diào)整多陣列系統(tǒng)中不同的 SYNC 傳遞時間變成了一個可以忽略的小問題。這是光纖解決方案的優(yōu)點之一。

完全速率鏈接鎖定

成功與否取決于兩個因素。第一個因素是編碼引擎的數(shù)字設(shè)計所固有的。此外,編碼引擎依賴于嵌入式 PLL 以區(qū)分時鐘沿和同步到參考時鐘。

外部到編碼引擎的部分與光纖鏈接的特性有關(guān)。在較大的數(shù)據(jù)率范圍里,鏈路的性能有所不同。因此,光纖收發(fā)器需提供內(nèi)部的電流調(diào)制控制。我們還未測試樣機的這方面的特性,將在評估性能隨溫度變化的特性時進一步研究。

到目前為止的成果

盡管我們進行了大量的數(shù)字模擬,但還需在硬件就位并準備好上電后,進行實際的操作驗證。也許盡管經(jīng)過了一輪嚴格的檢查,最初的設(shè)計還是存在一些微小的硬件錯誤,需要進一步修改和調(diào)整。

第一次上電令人失望。盡管我們進行了大量的模擬工作,但事實證明,尋找阻礙接收端鎖定參考時鐘的原因是一件非常具有挑戰(zhàn)性的工作。我們開始懷疑接收的串行參考時鐘的質(zhì)量。當我們將參考時鐘速率從 EV12AQ600標稱的最大 12.8Gbps 線速率大幅降 低 至 9.0Gbps (4.5GHz 參考時鐘),終于出現(xiàn)了令人期待的鏈接鎖定。

雖然這時 ADC 輸出數(shù)據(jù)速率只有期望最大值的三分之二左右,但令我們滿意的是,我們已經(jīng)建立了鎖定的鏈路,未來可通過調(diào)整參考時鐘和優(yōu)化鏈接特性實現(xiàn)目標性能。在建立鎖定的過程中,我們確認了幾個關(guān)鍵的鏈接參數(shù),從而驗證了這個樣機的核心假設(shè),具體有以下幾點:

- 多通道光纖鏈路解決方案可提供一個可行的結(jié)合了低速控制信號和高速數(shù)字信號的傳輸層

- 編碼和解碼解決方案需支持所需的所有接口信號需求,至少是當前光纖收發(fā)器正常工作所需的所有信號

- 關(guān)鍵的 SYNC 信號的成功編碼和解碼。這可為未來的相位陣列無線電設(shè)計提供支持。

- 光纖完全支持無線電模擬前端和數(shù)字信號處理后端的物理分隔

結(jié)論

盡快我們沒有實現(xiàn)全速的數(shù)據(jù)信號,但這個使用超過 10米的光纖的實驗設(shè)計已被證明是可靠的,雖然它的數(shù)據(jù)率比目標值低一些。此外,一旦建立了鏈接同步,樣機就可不間斷地運行,并且不會丟失鏈接鎖定或改變比特錯誤率(BER)。更棒的是,我們使用 Radiall 光纖收發(fā)器 為光纖調(diào)制電流提數(shù)字控制,可進一步調(diào)整光纖傳輸特性。我們確信,通過進一步的優(yōu)化,數(shù)據(jù)傳輸?shù)哪芰M一步增強,從而實現(xiàn)全速 12.8Gbps 的傳輸。

在我們宣稱實驗成功之前,有幾個重要的問題需要進一步的驗證。其中最重要的問題是驗證更廣泛的系統(tǒng)級確定性多通道操作的可行性,而不是簡單的單接收的SYNC 解碼。此外,這個問題的結(jié)論適用于不同的環(huán)境條件——特別是溫度和電壓變化的情況。

時間會證明一切,但至少迄今為止的進展是令人鼓舞的。現(xiàn)在,我們正站在向先進的數(shù)字智能微波天線設(shè)計的主要解決方案轉(zhuǎn)變的邊緣。

相關(guān)新聞

- ? 算力底座加速升級,我國工業(yè)互聯(lián)網(wǎng)實現(xiàn) 41 個工業(yè)大類全覆蓋

- ? 海爾集團收購新時達完成股權(quán)交割,深耕卡奧斯工業(yè)互聯(lián)網(wǎng)生態(tài)

- ? 一鍵“通關(guān)”數(shù)字化!卡奧斯企業(yè)級工業(yè)互聯(lián)網(wǎng)平臺2025版發(fā)布

- ? 工業(yè)互聯(lián)網(wǎng)平臺邊緣管理國家標準公開征求意見

- ? 蟬聯(lián)《中國500最具價值品牌》行業(yè)首位,卡奧斯以AI驅(qū)動品牌增長

- ? 京津冀網(wǎng)絡(luò)安全和工業(yè)互聯(lián)網(wǎng)產(chǎn)業(yè)聚集企業(yè)超2000家 產(chǎn)業(yè)規(guī)模穩(wěn)居全國第一梯隊

- ? 中國工業(yè)互聯(lián)網(wǎng)研究院發(fā)布《全國主要城市工業(yè)互聯(lián)網(wǎng)發(fā)展指數(shù)報告》

- ? 卡奧斯與云圖控股,全面合作簽約!

- ? 賽意信息擬3.3億元投建加碼研發(fā) 5名實控人多次減持累套現(xiàn)約7億元

- ? 成功入選!卡奧斯AI助力三大行業(yè)實現(xiàn)智能化轉(zhuǎn)型

編輯精選

- ? PLC市場穩(wěn)定回暖,國產(chǎn)化進程加速推進

- ? 鴻道操作系統(tǒng)在京首發(fā) 突破“大小腦”核心技術(shù)開啟自主可控具身智能新紀元

- ? 2025年施耐德電氣創(chuàng)新峰會盛大開幕

- ? ABB 加速器中國周為創(chuàng)新加速

- ? 羅克韋爾自動化發(fā)布第十版《智能制造現(xiàn)狀報告》

- ? 西門子舉辦“Realize LIVE”大會

- ? 埃夫特牽頭成立 “高速高精技術(shù)創(chuàng)新聯(lián)合體”,助力長三角一體化發(fā)展

- ? 匯川技術(shù)分拆聯(lián)合動力上市,關(guān)聯(lián)交易增收引關(guān)注

- ? 東土科技參與國家重點研發(fā)計劃 ,共同研發(fā)工業(yè)智控創(chuàng)新技術(shù)

- ? 2025華南國際工業(yè)博覽會圓滿閉幕

工控原創(chuàng)

- ? 一文get六月工控自動化大事

- ? ABB加速器中國周:當AI邂逅硬核工業(yè),一場自下而上的智造革命

- ? 點擊了解5月工控圈那些事兒

- ? 分拆上市還是出售?ABB機器人業(yè)務(wù)將何去何從

- ? 打造標桿案例及生態(tài)圈,ABB全力推動Ethernet-APL應(yīng)用加速

- ? 你關(guān)心的四月份工控大事全在這里

- ? 匯川技術(shù)2024年財報解析:多元化布局彰顯增長韌性

- ? 關(guān)稅政策讓美國工業(yè)自動化復(fù)蘇之路面臨不確定性

- ? ADI系統(tǒng)級創(chuàng)新方案深度賦能工業(yè)智能化與能源安全

- ? 32篇新聞,帶你回顧3月工控圈熱點